# Parallel Computing in Quantum Chemistry

Curtis L. Janssen

lda M. B. Nielsen

# Parallel Computing in Quantum Chemistry

# Parallel Computing in Quantum Chemistry

Curtis L. Janssen Ida M. B. Nielsen

This manuscript has been authored by Sandia National Laboratories, Contract No. DE-AC04-94AL85000 with the U.S. Department of Energy and Limit Point Systems, Inc. subcontract LF-5537 with Sandia. The publisher, by accepting the manuscript for publication, acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes.

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2008 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-13: 978-1-4200-5164-3 (Hardcover)

This book contains information obtained from authentic and highly regarded sources Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The Authors and Publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www. copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Janssen, Curtis L.

Parallel computing in quantum chemistry / Curtis L. Janssen and Ida M.B. Nielsen.

p. cm.

Includes bibliographical references and index.

ISBN 978-1-4200-5164-3 (acid-free paper)

1. Quantum chemistry--Data processing. 2. Parallel programming (Computer science) 3. Parallel processing (Electronic computers) I. Nielsen, Ida M. B. II. Title.

QD462.6.D38J36 2008 541'.280285435--dc22

2007048052

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

# **Contents**

# I Parallel Computing Concepts and Terminology

| 1.2 Trends in Hardware Development 1.2.1 Moore's Law 1.2.2 Clock Speed and Performance 1.2.3 Bandwidth and Latency 1.2.4 Supercomputer Performance 1.3 Trends in Parallel Software Development 1.3.1 Responding to Changes in Hardware 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring. 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy | 1 | Intr | oducti   | on                                                   | 3    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----------|------------------------------------------------------|------|

| 1.2.1 Moore's Law 1.2.2 Clock Speed and Performance 1.2.3 Bandwidth and Latency 1.2.4 Supercomputer Performance 1.3 Trends in Parallel Software Development 1.3.1 Responding to Changes in Hardware 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring. 2.2.4.3 Mesh and Torus 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy             |   | 1.1  | Parall   | lel Computing in Quantum Chemistry: Past and Present | 4    |

| 1.2.2 Clock Speed and Performance 1.2.3 Bandwidth and Latency 1.2.4 Supercomputer Performance 1.3 Trends in Parallel Software Development 1.3.1 Responding to Changes in Hardware 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                            |   | 1.2  | Trend    | ls in Hardware Development                           | 5    |

| 1.2.2 Clock Speed and Performance 1.2.3 Bandwidth and Latency 1.2.4 Supercomputer Performance 1.3 Trends in Parallel Software Development 1.3.1 Responding to Changes in Hardware 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                            |   |      | 1.2.1    | Moore's Law                                          | 5    |

| 1.2.3 Bandwidth and Latency 1.2.4 Supercomputer Performance 1.3 Trends in Parallel Software Development. 1.3.1 Responding to Changes in Hardware 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                        |   |      | 1.2.2    | Clock Speed and Performance                          |      |

| 1.3 Trends in Parallel Software Development.  1.3.1 Responding to Changes in Hardware.  1.3.2 New Algorithms and Methods.  1.3.3 New Programming Models. References.  2 Parallel Computer Architectures.  2.1 Flynn's Classification Scheme.  2.1.1 Single-Instruction, Single-Data.  2.1.2 Single-Instruction, Multiple-Data.  2.1.3 Multiple-Instruction, Multiple-Data.  2.1.4 Direct and Indirect Networks.  2.2.1 Direct and Indirect Networks.  2.2.2 Routing.  2.2.3 Network Performance.  2.2.4 Network Topology.  2.2.4.1 Crossbar  2.2.4.2 Ring.  2.2.4.3 Mesh and Torus.  2.2.4.4 Hypercube.  2.2.4.5 Fat Tree.  2.2.4.6 Bus.  2.2.4.7 Ad Hoc Grid.  2.3 Node Architecture.  2.4 MIMD System Architecture.  2.4.1 Memory Hierarchy.                                                                    |   |      | 1.2.3    | Bandwidth and Latency                                | 7    |

| 1.3.1 Responding to Changes in Hardware. 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme. 2.1.1 Single-Instruction, Single-Data. 2.1.2 Single-Instruction, Multiple-Data. 2.1.3 Multiple-Instruction, Multiple-Data. 2.1.4 Direct and Indirect Networks. 2.2.1 Direct and Indirect Networks. 2.2.2 Routing. 2.2.3 Network Performance. 2.2.4 Network Topology. 2.2.4.1 Crossbar 2.2.4.2 Ring. 2.2.4.3 Mesh and Torus. 2.2.4.4 Hypercube. 2.2.4.5 Fat Tree. 2.2.4.6 Bus. 2.2.4.7 Ad Hoc Grid. 2.3 Node Architecture. 2.4 MIMD System Architecture. 2.4.1 Memory Hierarchy.                                                                                                                                           |   |      | 1.2.4    | Supercomputer Performance                            |      |

| 1.3.1 Responding to Changes in Hardware. 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme. 2.1.1 Single-Instruction, Single-Data. 2.1.2 Single-Instruction, Multiple-Data. 2.1.3 Multiple-Instruction, Multiple-Data. 2.1.4 Direct and Indirect Networks. 2.2.1 Direct and Indirect Networks. 2.2.2 Routing. 2.2.3 Network Performance. 2.2.4 Network Topology. 2.2.4.1 Crossbar 2.2.4.2 Ring. 2.2.4.3 Mesh and Torus. 2.2.4.4 Hypercube. 2.2.4.5 Fat Tree. 2.2.4.6 Bus. 2.2.4.7 Ad Hoc Grid. 2.3 Node Architecture. 2.4 MIMD System Architecture. 2.4.1 Memory Hierarchy.                                                                                                                                           |   | 1.3  | Trend    | ls in Parallel Software Development                  | .10  |

| 1.3.2 New Algorithms and Methods 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.1.4 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                              |   |      |          | Responding to Changes in Hardware                    |      |

| 1.3.3 New Programming Models References  2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                 |   |      | 1.3.2    | New Algorithms and Methods                           |      |

| 2 Parallel Computer Architectures 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                             |   |      | 1.3.3    | New Programming Models                               |      |

| 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                               |   | Refe | erences  |                                                      | . 13 |

| 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                               |   |      |          |                                                      |      |

| 2.1 Flynn's Classification Scheme 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                               | 2 | Para | allel Co | omputer Architectures                                | . 17 |

| 2.1.1 Single-Instruction, Single-Data 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                 |   |      | Flynn    | 's Classification Scheme                             | . 17 |

| 2.1.2 Single-Instruction, Multiple-Data 2.1.3 Multiple-Instruction, Multiple-Data 2.2 Network Architecture 2.2.1 Direct and Indirect Networks 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                       |   |      | -        | Single-Instruction, Single-Data                      |      |

| 2.1.3 Multiple-Instruction, Multiple-Data  2.2 Network Architecture.  2.2.1 Direct and Indirect Networks.  2.2.2 Routing.  2.2.3 Network Performance.  2.2.4 Network Topology.  2.2.4.1 Crossbar  2.2.4.2 Ring.  2.2.4.3 Mesh and Torus  2.2.4.4 Hypercube.  2.2.4.5 Fat Tree  2.2.4.6 Bus.  2.2.4.7 Ad Hoc Grid  2.3 Node Architecture  2.4 MIMD System Architecture  2.4.1 Memory Hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 2.1.2    | Single-Instruction, Multiple-Data                    |      |

| 2.2 Network Architecture  2.2.1 Direct and Indirect Networks  2.2.2 Routing  2.2.3 Network Performance  2.2.4 Network Topology  2.2.4.1 Crossbar  2.2.4.2 Ring  2.2.4.3 Mesh and Torus  2.2.4.4 Hypercube  2.2.4.5 Fat Tree  2.2.4.6 Bus  2.2.4.7 Ad Hoc Grid  2.3 Node Architecture  2.4 MIMD System Architecture  2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | 2.1.3    | Multiple-Instruction, Multiple-Data                  |      |

| 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 2.2  | Netw     | ork Architecture                                     |      |

| 2.2.2 Routing 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      | 2.2.1    | Direct and Indirect Networks                         | .19  |

| 2.2.3 Network Performance 2.2.4 Network Topology 2.2.4.1 Crossbar 2.2.4.2 Ring 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 2.2.2    | Routing                                              |      |

| 2.2.4 Network Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 2.2.3    | Network Performance                                  |      |

| 2.2.4.1 Crossbar  2.2.4.2 Ring.  2.2.4.3 Mesh and Torus  2.2.4.4 Hypercube.  2.2.4.5 Fat Tree  2.2.4.6 Bus.  2.2.4.7 Ad Hoc Grid  2.3 Node Architecture  2.4 MIMD System Architecture  2.4.1 Memory Hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 2.2.4    | Network Topology                                     |      |

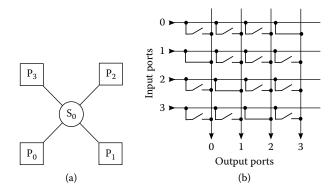

| 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |          | 2.2.4.1 Crossbar                                     |      |

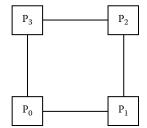

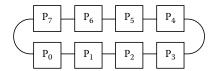

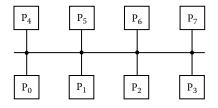

| 2.2.4.3 Mesh and Torus 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |          | 2.2.4.2 Ring                                         | .27  |

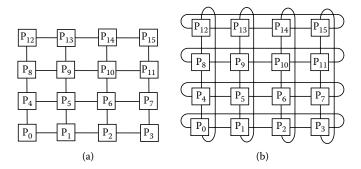

| 2.2.4.4 Hypercube 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |          |                                                      |      |

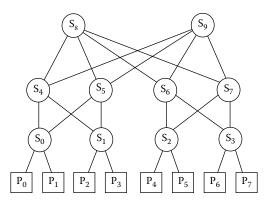

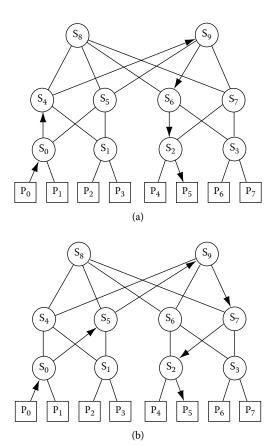

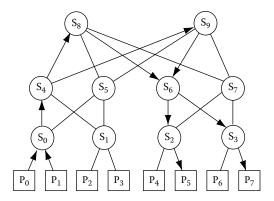

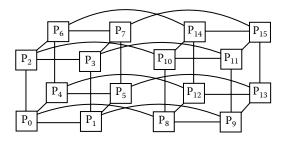

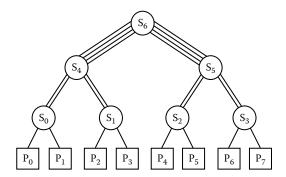

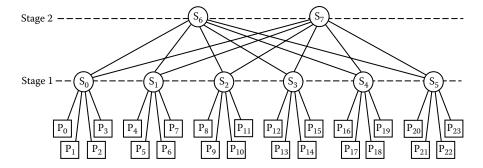

| 2.2.4.5 Fat Tree 2.2.4.6 Bus 2.2.4.7 Ad Hoc Grid 2.3 Node Architecture 2.4 MIMD System Architecture 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |          |                                                      |      |

| 2.2.4.7 Ad Hoc Grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |          |                                                      |      |

| <ul><li>2.3 Node Architecture</li><li>2.4 MIMD System Architecture</li><li>2.4.1 Memory Hierarchy</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |          | 2.2.4.6 Bus                                          | .30  |

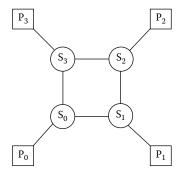

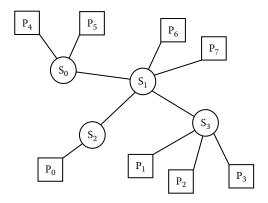

| <ul><li>2.3 Node Architecture</li><li>2.4 MIMD System Architecture</li><li>2.4.1 Memory Hierarchy</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |          | 2.2.4.7 Ad Hoc Grid                                  | . 31 |

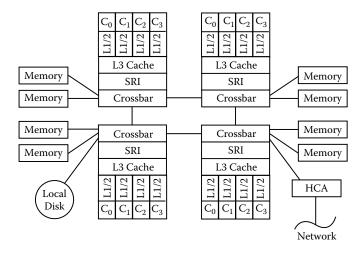

| 2.4 MIMD System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 2.3  | Node     | Architecture                                         |      |

| 2.4.1 Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 2.4  |          | D System Architecture                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |          | Memory Hierarchy                                     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      | 2.4.2    | Persistent Storage                                   |      |

|   |      | 2.4.2.1 Local Storage                                     | 37  |

|---|------|-----------------------------------------------------------|-----|

|   |      | 2.4.2.2 Network Storage                                   |     |

|   |      | 2.4.2.3 Trends in Storage                                 | 38  |

|   |      | 2.4.3 Reliability                                         |     |

|   |      | 2.4.4 Homogeneity and Heterogeneity                       |     |

|   |      | 2.4.5 Commodity versus Custom Computers                   |     |

|   | 2.5  | Further Reading                                           |     |

|   | Refe | erences                                                   | 43  |

| 3 | Con  | nmunication via Message-Passing                           | 45  |

| _ | 3.1  | Point-to-Point Communication Operations                   |     |

|   | 0.1  | 3.1.1 Blocking Point-to-Point Operations                  |     |

|   |      | 3.1.2 Non-Blocking Point-to-Point Operations              |     |

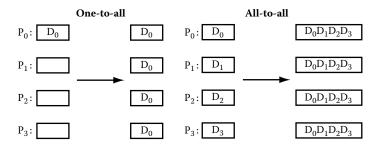

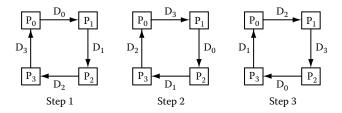

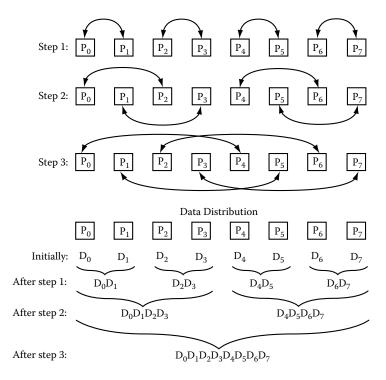

|   | 3.2  | Collective Communication Operations                       |     |

|   | ٠    | 3.2.1 One-to-All Broadcast                                |     |

|   |      | 3.2.2 All-to-All Broadcast                                |     |

|   |      | 3.2.3 All-to-One Reduction and All-Reduce                 |     |

|   | 3.3  | One-Sided Communication Operations                        |     |

|   | 3.4  | Further Reading                                           |     |

|   | _    | erences                                                   |     |

|   |      |                                                           |     |

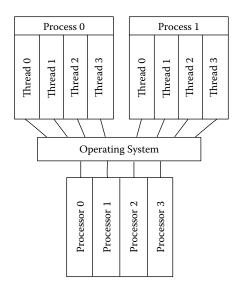

| 4 |      | lti-Threading                                             |     |

|   | 4.1  | Pitfalls of Multi-Threading                               |     |

|   | 4.2  | Thread-Safety                                             |     |

|   | 4.3  | Comparison of Multi-Threading and Message-Passing         | 65  |

|   | 4.4  | Hybrid Programming                                        | 66  |

|   | 4.5  | Further Reading                                           |     |

|   | Refe | erences                                                   | 70  |

| 5 | Para | allel Performance Evaluation                              | 71  |

|   | 5.1  | Network Performance Characteristics                       |     |

|   | 5.2  | Performance Measures for Parallel Programs                |     |

|   | ٠    | 5.2.1 Speedup and Efficiency                              |     |

|   |      | 5.2.2 Scalability                                         |     |

|   | 5.3  | Performance Modeling                                      |     |

|   | 0.0  | 5.3.1 Modeling the Execution Time                         |     |

|   |      | 5.3.2 Performance Model Example: Matrix-Vector            | 00  |

|   |      | Multiplication                                            | 83  |

|   | 5.4  | Presenting and Evaluating Performance Data: A Few Caveats |     |

|   | 5.5  | Further Reading                                           |     |

|   |      | erences                                                   |     |

| _ |      |                                                           |     |

| 6 |      | allel Program Design                                      |     |

|   | 6.1  | Distribution of Work                                      |     |

|   |      | 6.1.1 Static Task Distribution                            | .95 |

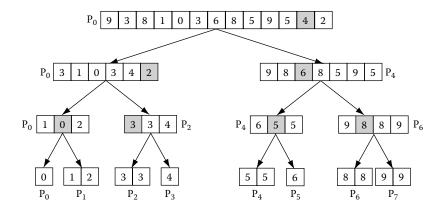

|   |      | 6.1.1.1 Round-Robin and Recursive                         |     |

|   |      | Task Distributions                                        | 96  |

|    |      | 6.1.2   | Dynam           | ic Task Distribution                             | 99   |

|----|------|---------|-----------------|--------------------------------------------------|------|

|    |      |         | 6.1.2.1         |                                                  |      |

|    |      |         | 6.1.2.2         | Decentralized Task Distribution                  | 101  |

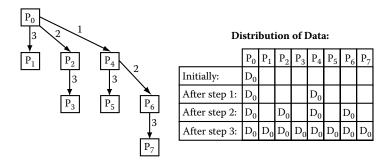

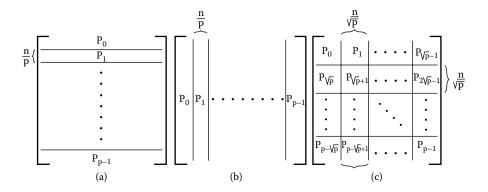

|    | 6.2  | Distri  | bution o        | f Data                                           | 101  |

|    | 6.3  | Desig   | ning a C        | ommunication Scheme                              | 104  |

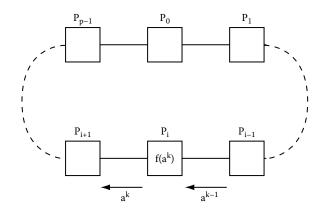

|    |      | 6.3.1   | Using C         | Collective Communication                         | 104  |

|    |      | 6.3.2   | Using F         | Point-to-Point Communication                     | 105  |

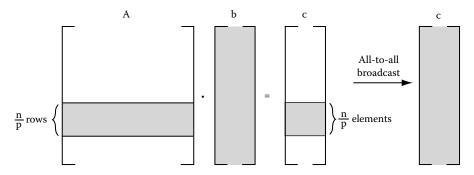

|    | 6.4  | Desig   | n Examp         | ole: Matrix-Vector Multiplication                | 107  |

|    |      | 6.4.1   | Using a         | Row-Distributed Matrix                           | 108  |

|    |      | 6.4.2   | Using a         | Block-Distributed Matrix                         | 109  |

|    | 6.5  | Sumn    | nary of K       | Key Points of Parallel Program Design            | 112  |

|    | 6.6  | Furth   | er Readi        | ng                                               | 114  |

|    | Refe | erences |                 |                                                  | 114  |

| II | -    | -       |                 | Parallel Programming in Quantum Cho              |      |

| 7  |      |         |                 | gral Evaluation                                  |      |

|    | 7.1  |         |                 | ral Computation                                  |      |

|    | 7.2  |         |                 | mentation Using Static Load Balancing            | 119  |

|    |      | 7.2.1   |                 | Algorithms Distributing Shell Quartets           |      |

|    |      |         |                 | irs                                              |      |

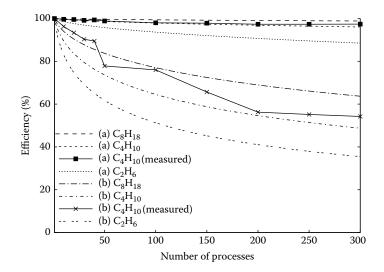

|    |      | 7.2.2   |                 | nance Analysis                                   | 121  |

|    |      |         | 7.2.2.1         | Determination of the Load Imbalance              |      |

|    |      |         |                 | Factor $k(p)$                                    | 122  |

|    |      |         | 7.2.2.2         | Determination of $\mu$ and $\sigma$ for Integral |      |

|    |      |         |                 | Computation                                      |      |

|    |      |         | 7.2.2.3         | Predicted and Measured Efficiencies              |      |

|    | 7.3  |         |                 | mentation Using Dynamic Load Balancing.          |      |

|    |      |         |                 | Algorithm Distributing Shell Pairs               |      |

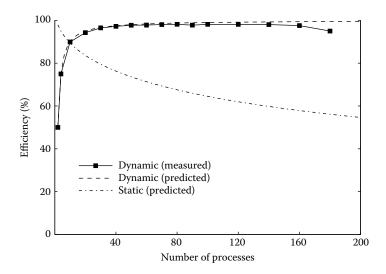

|    |      | 7.3.2   |                 | nance Analysis                                   |      |

|    |      |         |                 | Load Imbalance                                   |      |

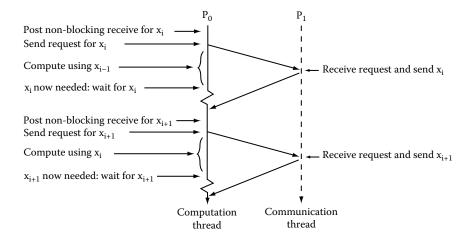

|    |      |         |                 | Communication Time                               |      |

|    |      |         |                 | Predicted and Measured Efficiencies              |      |

|    | Refe | erences |                 |                                                  | 130  |

| 8  | The  | Hartre  | o_Fock          | Method                                           | 131  |

| U  | 8.1  |         |                 | Fock Equations                                   |      |

|    | 8.2  |         |                 | Fock Procedure                                   |      |

|    | 8.3  |         |                 | Matrix Formation with Replicated Data            |      |

|    | 8.4  |         |                 | Matrix Formation with Distributed Data           |      |

|    |      |         |                 |                                                  |      |

|    | 8.5  |         |                 | ng                                               |      |

|    | Kete | erences | • • • • • • • • |                                                  | 146  |

| 9  | Sec  | ond-O   | rder Møl        | ler–Plesset Perturbation Theory                  | 147  |

| -  | 9.1  |         |                 | MP2 Equations                                    |      |

|    | 9.2  |         |                 | et MP2 Algorithm                                 |      |

|    | —    |         |                 | 0                                                | = => |

|              | 9.3 Parallelization with Minimal Modifications  | 151 |

|--------------|-------------------------------------------------|-----|

|              | 9.4 High-Performance Parallelization            | 154 |

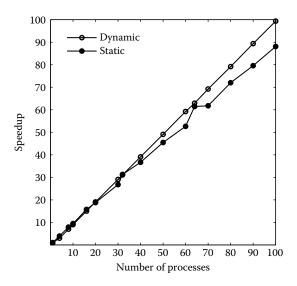

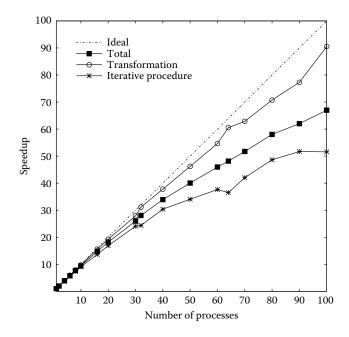

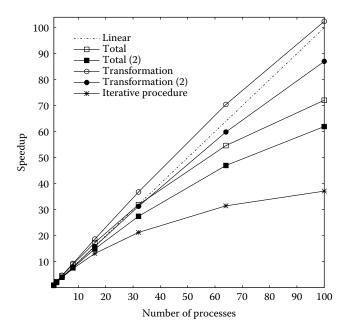

|              | 9.5 Performance of the Parallel Algorithms      |     |

|              | 9.6 Further Reading                             |     |

|              | References                                      |     |

|              |                                                 |     |

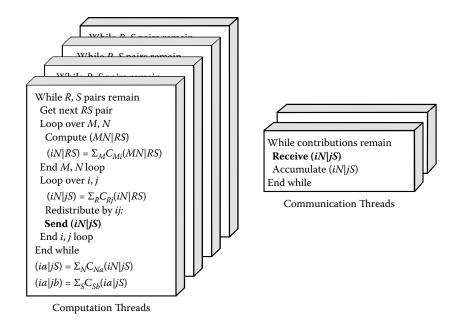

| 10           | Local Møller–Plesset Perturbation Theory        | 167 |

|              | 10.1 The LMP2 Equations                         |     |

|              | 10.2 A Scalar LMP2 Algorithm                    |     |

|              | 10.3 Parallel LMP2                              |     |

|              | 10.3.1 Two-Electron Integral Transformation     |     |

|              | 10.3.2 Computation of the Residual              |     |

|              | 10.3.3 Parallel Performance                     |     |

|              | References                                      |     |

|              |                                                 |     |

| Ar           | ppendices                                       |     |

| 1 <b>1</b> P | penalees                                        |     |

| Α            | A Brief Introduction to MPI                     | 191 |

| А            | A Difer introduction to will i                  | 101 |

| В            | Dilance les Families d'Thomas le                | 100 |

| D            | Pthreads: Explicit Use of Threads               | 189 |

| $\mathbf{c}$ |                                                 | 105 |

| C            | OpenMP: Compiler Extensions for Multi-Threading | 195 |

|              | 1                                               | 205 |

| Inc          | dex                                             | 205 |

# **Preface**

This book is intended to serve as a reference for the design and implementation of parallel quantum chemistry programs. Development of efficient quantum chemistry software capable of utilizing large-scale parallel computers requires a grasp of many issues pertaining to both parallel computing hardware and parallel programming practices, as well as an understanding of the methods to be implemented. The text provides an in-depth view of parallel programming challenges from the perspective of a quantum chemist, including parallel computer architectures, message-passing, multi-threading, parallel program design and performance analysis, as well as parallel implementation of important electronic structure procedures and methods such as two-electron integral computation, Hartree-Fock and second-order Møller-Plesset perturbation (MP2) theory, and the local correlation method LMP2. Some topics relevant to parallel computing in quantum chemistry have not been included in this book. Thus, performance tools and debuggers are not treated, parallel I/O is only briefly discussed, and advanced electronic structure methods such as coupled-cluster theory and configuration interaction are not covered.

We will assume that the reader has a basic understanding of quantum chemistry, including Hartree–Fock theory and correlated electronic structure methods such as Møller–Plesset perturbation theory. Readers can find introductory discussions of these methods in, for example, Jensen<sup>1</sup> and the classic Szabo and Ostlund text.<sup>2</sup> A comprehensive and somewhat more advanced treatment of electronic structure theory can be found in Helgaker, Jørgensen, and Olsen.<sup>3</sup> No prior experience with parallel computing is required, but the reader should be familiar with computer programming and programming languages at the advanced undergraduate level. The program examples in the book are written in the C programming language, and at least a rudimentary knowledge of C will therefore be helpful. The text by Kernighan and Ritchie<sup>4</sup> covers all C features used in this book.

# Scope and Organization of the Text

This book is divided into two parts. In Part I we will discuss parallel computer architectures as well as parallel computing concepts and terminology with a focus on good parallel program design and performance

analysis. Part II contains detailed discussions and performance analyses of parallel algorithms for a number of important and widely used quantum chemistry procedures and methods.

An outline of the contents of each chapter is given below.

#### Chapter 1: Introduction

Here we provide a brief history of parallel computing in quantum chemistry and discuss trends in hardware as well as trends in the methods and algorithms of quantum chemistry. The impact of these trends on future quantum chemistry programs will be considered.

## Chapter 2: Parallel Computer Architectures

This chapter provides an overview of parallel computer architectures, including the traditional Flynn classification scheme and a discussion of computation nodes and the networks connecting them. We also present an overall system view of a parallel computer, describing the hierarchical nature of parallel architecture, machine reliability, and the distinction between commodity and custom computers.

# Chapter 3: Communication via Message-Passing

This chapter covers message-passing, one of the primary software tools required to develop parallel quantum chemistry programs for distributed memory parallel computers. Point-to-point, collective, and one-sided varieties of message-passing are also discussed.

# Chapter 4: Multi-Threading

The importance of multi-threading will continue to increase due to the emergence of multicore chips. Parallelization by means of multi-threading is discussed as well as hybrid multi-threading/message-passing approaches for utilizing large-scale parallel computers.

# Chapter 5: Parallel Performance Evaluation

Design and implementation of efficient parallel algorithms requires careful analysis and evaluation of their performance. This chapter introduces idealized machine models along with measures for predicting and assessing the performance of parallel algorithms.

# Chapter 6: Parallel Program Design

This chapter discusses fundamental issues involved in designing and implementing parallel programs, including the distribution of tasks and data as well as schemes for interprocessor communication.

## Chapter 7: Two-Electron Integral Evaluation

An important, basic step performed in most quantum chemistry programs is the computation of the two-electron integrals. Schemes for parallel computation of these integrals and detailed performance models incorporating load imbalance are discussed.

## Chapter 8: The Hartree-Fock Method

The Hartree–Fock method is central to quantum chemistry, and an efficient Hartree–Fock program is an essential part of a quantum chemistry program package. We outline the Hartree–Fock procedure and present and analyze both replicated data and distributed data Fock matrix formation algorithms.

## Chapter 9: Second-Order Møller–Plesset Perturbation Theory

Second-order Møller–Plesset (MP2) perturbation theory is a widely used quantum chemical method for incorporating electron correlation. This chapter considers parallel computation of MP2 energies, comparing the performance achievable with simple and more sophisticated parallelization strategies.

# Chapter 10: Local Møller-Plesset Perturbation Theory

Local correlation methods represent an important new class of correlated electronic structure methods that aim at computing molecular properties with the same accuracy as their conventional counterparts but at a significantly lower computational cost. We discuss the challenges of parallelizing local correlation methods in the context of local second-order Møller–Plesset perturbation theory, illustrating a parallel implementation and presenting benchmarks as well.

# Appendix A: A Brief Introduction to MPI

The Message-Passing Interface (MPI) is the primary mechanism used for explicit message-passing in scientific computing applications. This appendix briefly discusses some of the most commonly used MPI routines.

# Appendix B: Pthreads

Pthreads is a standard for creating and managing multiple threads. We give a brief introduction to multi-threaded programming with Pthreads, including an example Pthreads program.

# Appendix C: OpenMP

OpenMP is a set of compiler extensions to facilitate development of multithreaded programs. We describe these compiler extensions, using example source code illustrating parallel programming with OpenMP.

# References

- 1. Jensen, F. *Introduction to Computational Chemistry*. Chichester, UK: John Wiley & Sons, 1999.

- 2. Szabo, A., and N. S. Ostlund. *Modern Quantum Chemistry*, 1st revised edition. New York: McGraw-Hill, 1989.

- 3. Helgaker, T., P. Jørgensen, and J. Olsen. *Molecular Electronic-Structure Theory*. Chichester, UK: John Wiley & Sons, 2000.

- 4. Kernighan, B. W., and D. M. Ritchie. *The C Programming Language*, 2nd edition. Englewood Cliffs, NJ: Prentice Hall, 1988.

# Acknowledgments

We are indebted to many people who provided support and advice in the preparation of this book. Lance Wobus of Taylor & Francis encouraged us to undertake the writing of the book, and Jennifer Smith expertly guided us through the final stages of manuscript preparation. We thank Craig Smith and Kurt Olsen at Sandia National Laboratories for facilitating the project, and we appreciate the assistance of Gregg Andreski, who prepared most of the artwork. Jan Linderberg kindly provided historical references, and Shawn Brown, Joe Kenny, and Matt Leininger made insightful comments on various drafts of the manuscript. Ron Minnich, Helgi Adalsteinsson, Jim Schutt, Ed Valeev, Daniel Crawford, Theresa Windus, and David Bernholdt provided stimulating discussions, feedback, and technical data. Finally, CLJ would like to thank Mike Colvin for introducing him to parallel computing.

# **Funding Statement**

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

# **Authors**

**Curtis L. Janssen** is a Distinguished Member of the Technical Staff at Sandia National Laboratories and holds a Ph.D. in theoretical chemistry from the University of California at Berkeley. He has an extensive publication record in the areas of quantum chemistry methods development and high-performance computing, and he is the lead developer of the MPQC program suite.

Curtis L. Janssen Sandia National Laboratories 7011 East Ave. Livermore, CA 94550 cljanss@sandia.gov

**Ida M. B. Nielsen** is a scientist at Sandia National Laboratories and holds a Ph.D. in theoretical chemistry from Stanford University. She has published numerous articles on the development and application of quantum chemical methods and high-performance computing and is one of the core developers of the MPQC program suite.

Ida M. B. Nielsen Sandia National Laboratories 7011 East Ave. Livermore, CA 94550 ibniels@sandia.gov

# Disclaimer of Liability

This work of authorship was prepared as an account of work sponsored by an agency of the United States Government. Accordingly, the United States Government retains a nonexclusive, royalty-free license to publish or reproduce the published form of this contribution, or allow others to do so for United States Government purposes. Neither Sandia Corporation, the United States Government, nor any agency thereof, nor any of their employees makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately-owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by Sandia Corporation, the United States Government, or any agency thereof. The views and opinions expressed herein do not necessarily state or reflect those of Sandia Corporation, the United States Government, or any agency thereof.

#### **Trademarks**

Intel® and Intel® Xeon® are trademarks of Intel Corporation. AMD, AMD Opteron<sup>TM</sup>, and HyperTransport<sup>TM</sup> are trademarks of Advanced Micro Devices, Inc. Motorola® AltiVec<sup>TM</sup> is a trademark of Motorola, Inc. IBM POWER<sup>TM</sup> is a trademark of International Business Machines Corporation. Cray X1<sup>TM</sup> and Cray XT3<sup>TM</sup> are trademarks of Cray Inc. The Linux® trademark is owned by Linus Torvalds. InfiniBand<sup>TM</sup> is a trademark of the InfiniBand Trade Association. InfiniHost<sup>TM</sup> and InfiniScale<sup>TM</sup> are trademarks of Mellanox Technologies. Java<sup>TM</sup> is a trademark of Sun Microsystems Inc. OpenMP<sup>TM</sup> is a trademark of the OpenMP Architecture Review Board. UNIX<sup>TM</sup> is a trademark of The Open Group. POSIX® is a trademark of the Institute of Electrical and Electronic Engineers (IEEE). Myrinet® is a trademark of Myricom, Inc. Quadrics® is a trademark of Quadrics Ltd.

# Part I

# Parallel Computing Concepts and Terminology

# Introduction

The need for parallel software for scientific computing is ever increasing. Supercomputers are not only being built with more processors, but parallel computers are also no longer limited to large machines owned and managed by high-performance computing centers; parallel desktop computers are increasingly widespread, and even laptop computers have multiple processors. Development of scientific computing software must adapt to these conditions as parallel computation becomes the norm rather than the exception. In the field of quantum chemistry, additional factors contribute to the need for parallelism. Quantum chemistry has become an indispensable tool for investigating chemical phenomena, and quantum chemical methods are employed widely in research across many chemical disciplines; this widespread use of quantum chemistry reinforces the importance of rapid turnaround computations, which can be addressed by parallel computing. Additionally, for quantum chemistry to continue to be an integral part of chemical research, quantum chemical methods must be applicable to the chemical systems of interest, including larger molecules, and parallelism can play an important role in extending the range of these methods. Parallel implementations can broaden the scope of conventional quantum chemical methods, whose computational cost scales as a high-degree polynomial in the molecular size, and enable the treatment of very large molecular systems with linear-scaling or reduced-scaling methods.

In the following, we will first give a brief historical sketch and current perspective of parallel computing in quantum chemistry. We will then discuss trends in hardware development for single-processor and parallel computers as well as trends in parallel software development, including the parallel programming challenges following the emergence of new quantum chemical methods and the changes in hardware.

# 1.1 Parallel Computing in Quantum Chemistry: Past and Present

Although the history of parallel computing in quantum chemistry is closely linked to the development of parallel computers, the concept of parallel computing was utilized in quantum chemistry even before the introduction of electronic computers into the field. In the late 1940s and early 1950s, intrigued by the idea of parallel computations, Per-Olov Löwdin in Uppsala organized a group of graduate students to carry out numerical integrations using FACIT Electric desk calculators. In six months, this "parallel computer" evaluated more than 10,000 multicenter integrals, employing Simpson's rule with a correction term. These integrals allowed the computation of wave functions that made it possible to explain the cohesive and elastic properties as well as the behavior under very high pressure of a large number of alkali halides. <sup>1,2</sup>

The use of parallel *electronic* computers in quantum chemistry, however, was not explored until several decades later. Work by Clementi and coworkers<sup>3</sup> in the early 1980s demonstrated the use of a loosely coupled array of processors (with 10 compute processors) for computation of Hartree-Fock energies for a short DNA fragment. The Hartree-Fock computations for this 87-atom system, using a basis set with 315 basis functions, represented an extraordinary feat at the time. Other early work exploring the use of parallel computers in quantum chemistry include parallel implementations of both the Hartree-Fock method and a few correlated electronic structure methods. Thus, by the late 1980s, parallel programs had been developed for computation of Hartree-Fock energies <sup>4,5</sup> and gradients, <sup>6</sup> transformation of the two-electron integrals, <sup>4,5,7</sup> and computation of energies with second-order Møller-Plesset perturbation theory <sup>5,8</sup> (MP2) and the configuration interaction (CI) method. <sup>4</sup>

To a large extent, these pioneering efforts employed custom-built parallel computers such as the loosely coupled arrays of processors (LCAP), <sup>3,4,6,8</sup> although one of the early commercially available parallel computers, the Intel hypercube, was used as well. <sup>5,7</sup> In the late 1980s, the increasing availability of commercial parallel computers and the concomitant improvements in the requisite software, such as message-passing libraries, spurred many research groups to undertake development of parallel quantum chemistry applications. The development of parallel quantum chemistry methods, including the earliest efforts as well as later works carried out until the mid-1990s, has been reviewed elsewhere. <sup>9,10</sup> By the late 1990s, great strides had been made toward extending parallel computing in quantum chemistry to a wider range of methods and procedures, for instance, Hartree-Fock second derivatives, <sup>11</sup> MP2 gradients, <sup>12</sup> multireference CI, <sup>13</sup> multireference pseudospectral CI, <sup>14</sup> full CI, <sup>15</sup> and the coupled-cluster method. <sup>16,17</sup>

At present, parallel computing in quantum chemistry continues to be an active field of research; new and improved parallel algorithms for well-established quantum chemical methods are steadily appearing in the literature, and reports of new computational methods are often followed by Introduction 5

development of algorithms for their parallel execution. Examples of improved parallel algorithms for previously parallelized methods include a recent parallel implementation of the full CI method, <sup>18</sup> which enabled full CI calculations of an unprecedented size and provided valuable benchmark data, and a novel parallel implementation of the resolution-of-the-identity MP2 method, demonstrating computation of energies and gradients for large systems; <sup>19</sup> also, the first parallel implementation of the MP2-R12 method has been reported. <sup>20</sup> Furthermore, parallel algorithms have been developed for linear-scaling methods, for instance, linear-scaling computation of the Fock matrix, <sup>21,22</sup> which is the major computational step in Hartree-Fock and density functional theory, and the local MP2 method has been parallelized as well. <sup>23</sup> Additionally, new directions are being explored, such as automatic parallel code generation by the Tensor Contraction Engine<sup>24,25</sup> and utilization of multilevel parallelism to achieve improved parallel efficiency. <sup>26</sup>

These research efforts have resulted in a variety of quantum chemistry program packages with parallel capabilities; indeed, most quantum chemistry software suites today support some level of parallelism. A number of the parallel quantum chemistry program suites are freely available, and there are several commercial programs as well. Among the free program packages are: COLUMBUS, 27 which has parallelized versions of the multireference CI and multireference average quadratic coupled-cluster methods; DALTON,<sup>28</sup> which includes parallel Hartree-Fock and density functional theory (DFT); GAMESS (US), 29 with parallelized Hartree-Fock, DFT, and correlated wave functions, up to second derivatives for certain methods; MPQC, 30 designed to be parallel from the beginning, with parallel Hartree-Fock, DFT, and MP2 energies and gradients and parallel explicitly correlated MP2 energies; and NWChem, <sup>31</sup> also incorporating parallelism from the onset, supporting a wide range of methods including Hartree-Fock, DFT, time-dependent DFT, coupled-cluster methods, CI methods, as well as high-level methods for properties. Several commercial quantum chemistry program packages incorporate varying levels of parallelism; among these are ACES III, <sup>32</sup> GAMESS (UK), <sup>33</sup> Gaussian, <sup>34</sup> MOLCAS, <sup>35</sup> MOLPRO, <sup>36</sup> and Q-Chem. <sup>37</sup>

# 1.2 Trends in Hardware Development

Let us briefly look at some trends in hardware technology that have consequences for developers of parallel scientific applications and for the efficient utilization of single processors as well.

#### 1.2.1 Moore's Law

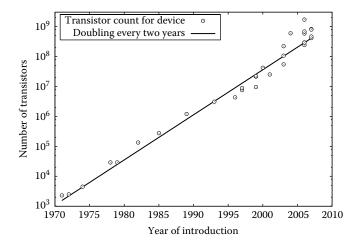

A central trend in hardware development is the exponential increase with time of the number of transistors in an integrated circuit. This observation, known as Moore's law, was first made in 1965 by Gordon Moore,<sup>38</sup> who found that the number of transistors that minimized the cost per component in an

**FIGURE 1.1** Historical development of the transistor count for integrated circuits. The solid line depicts Moore's 1975 prediction that transistor counts would double every two years. Data were obtained from Intel's web site, http://www.intel.com, and from Wikipedia, http://www.wikipedia.org.

integrated circuit was doubling every year and predicted that this trend would continue until 1975. In 1975, Moore updated his prediction,<sup>39</sup> estimating that the number of transistors in an integrated circuit would double every two years; three decades later, this trend still continues as illustrated in Figure 1.1.

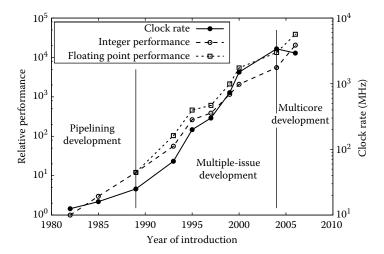

# 1.2.2 Clock Speed and Performance

The performance of an integrated circuit depends on the number of transistors, which has increased following Moore's law, and also on the clock speed, that is, the rate at which the circuit performs its most fundamental operations. Figure 1.2 shows the development over time of the integer and floating point performance of single chips along with the clock speeds of those chips. It is apparent from the figure that the performance improvement does not parallel that of the clock speed. The development of the clock speed relative to the instruction rate falls into three periods of chip development. The first period is distinguished by the use of *pipelining*, enabling instructions to be performed in several stages that are overlapped to improve performance. This is marked by the rapid improvement in performance relative to clock speed up until around 1989. During the second period, multiple-issue (or superscalar) processors were developed and improved. Such processors allow more than one instruction to start execution on each clock cycle. During this period the achieved performance gains were affected by a variety of factors, and the lack of equivalent gains in bandwidth and latency (discussed in the next section) resulted in an overall decrease in performance achieved per clock cycle. The third, and current, period is that of *multicore* processors. Clock speeds in these processors have dropped from their peak, yet significant performance

#### FIGURE 1.2

Development of clock rates, integer performance, and floating point performance for selected Intel chips from 1982 until the present. Integer performance data were normalized to a value of 1 for the first data point (1982); floating point performance data were normalized to make the first data point (1989) match the integer performance for that year. Integer performance was derived from SPECint92, SPECint95, SPECint2000, and SPECint2000rate benchmarks, <sup>50</sup> using the latest benchmark available for a given chip. For the oldest two chips, the maximum theoretical rate for instruction execution was employed, and the availability of several benchmarks for some processors allowed normalization of the data so that performance data from different benchmarks could be used. A similar approach was used for floating point performance using the floating point versions of the SPEC benchmarks. Data were obtained from Wikipedia, http://www.wikipedia.org; Intel's web site, http://www.intel.com; the SPEC web site, http://www.spec.org; and Hennessy and Patterson. <sup>51</sup> Various sources found with the Google news archive at http://news.google.com assisted in determining the year of introduction of each chip.

improvements are still realized by essentially completely replicating multiple processors on the same chip. The trend of placing multiple processors on a single integrated circuit is expected to continue for some time into the future.

# 1.2.3 Bandwidth and Latency

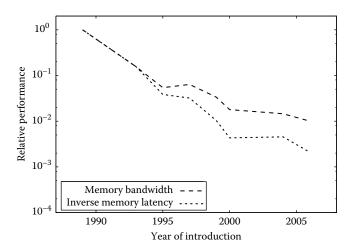

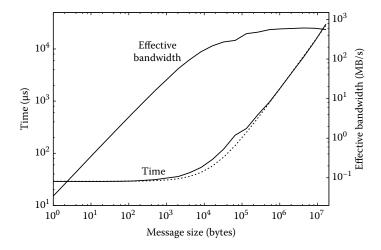

Important factors determining processor performance include the memory bandwidth and latency. The memory bandwidth is the rate at which a processor can transfer data to or from memory, and the memory latency is the time that elapses between a request for a data transfer and the arrival of the first datum. Figure 1.3 illustrates the development of the memory bandwidth and latency relative to the floating point performance over the last two decades. For any given year, the figure shows the ratio of the memory bandwidth and the inverse latency to the floating point performance, and both ratios have been normalized to yield a value of 1 in 1989; note that no absolute performance data can be gleaned from the figure. From the downward trends of the curves, however, it is clear that the improvements in latency lag the

FIGURE 1.3

Development of memory bandwidth and inverse latency relative to processor floating point performance from 1989 to the present. For a given year, the figure shows the memory bandwidth and inverse latency divided by the floating point performance, and the data are normalized to yield a value of 1 for 1989. Floating point performance data are identical to those reported in Figure 1.2; memory bandwidth and latency data were taken from Ref. 40 and, for recent years, obtained from Wikipedia, http://www.wikipedia.org, and with the assistance of the Google news archive, http://news.google.com.

improvements in bandwidth, which, in turn, are not as fast as the increase in the floating point performance. Similar trends are observed in bandwidths and latencies for networks and disks as well.<sup>40</sup>

To improve the bandwidth and reduce the latency, most modern processors can execute instructions out of order, permitting instructions to be scheduled ahead of those that are awaiting data. Also, a substantial portion of the available transistors on a chip are now dedicated to caches that hold frequently used data closer to the processor to reduce the latency penalty for each access. These measures, however, have not been sufficient to completely offset the effects of the relative decrease in the speeds of data movement. The much faster improvement in peak floating point computation rates compared to improvements in both memory and network bandwidth and latency have made efficient use of modern computers, in particular parallel computers, more challenging. For example, a parallel algorithm that had a negligible communication overhead when developed a decade ago may have a reduced parallel performance on today's computers because the faster improvement in floating point performance has made the communication time of the algorithm nonnegligible compared to the computation time.

# 1.2.4 Supercomputer Performance

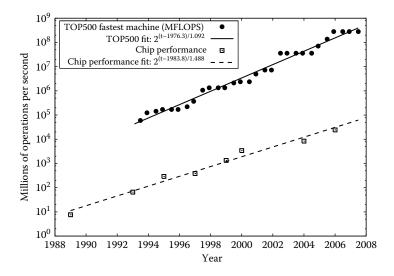

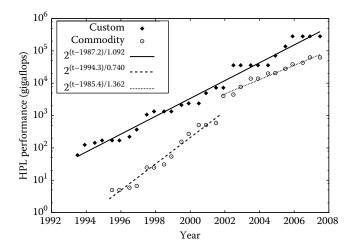

In addition to steady gains in the performance of a single chip, the speeds of the fastest parallel computers have shown tremendous growth. The TOP500

FIGURE 1.4 Semilogarithmic plot of the development over time of the speed of the world's fastest supercomputer and the floating point performance of a single chip. The speed of the fastest parallel computer doubles about every year, while the processing speed of a chip doubles about every eighteen months. The fastest supercomputer speed is measured as the floating point rate (in millions of floating point operations per second, MFLOPS) for the HPL benchmark for the computer at the top of the TOP500 list. <sup>41</sup> The single-chip floating point performance is normalized to the effective single-chip floating point performance in the HPL benchmark determined for the Sandia Thunderbird computer (described in section 2.4.5) for which both HPL and single-chip data were available.

list, <sup>41</sup> compiled every year since 1993, ranks the world's fastest parallel computers using the High-Performance Linpack benchmark <sup>42</sup> (HPL). Figure 1.4 shows the development over time of the speed of the fastest TOP500 computer and the floating point performance of the fastest single chip. The speed of the fastest parallel computer, doubling roughly every year, grows at a significantly faster rate than the speed of the fastest chip, which doubles about every eighteen months. This difference in growth rates is due mostly to the increase over the years in the total number of chips contained by the largest parallel computers. If these trends hold, the fastest TOP500 supercomputer will run at a speed of around 7 petaflops in the year 2012.

Regarding single-chip performance, given the stagnation in clock speeds shown in Figure 1.2, it is reasonable to expect that most of the on-chip improvements in the near future will be obtained by adding more processor cores. The 2006 chip performance data in Figure 1.4 were obtained for a two-core chip, and, extrapolating the trend in floating point performance improvements, we would then expect each chip to have around 32 processor cores in 2012. Alternatively, one might find that chip manufacturers would switch to more, but simpler, cores on a chip, and this could dramatically increase the number

of cores available. As a case in point, a research chip containing 80 cores was demonstrated by Intel in 2006.

# 1.3 Trends in Parallel Software Development

In the previous section we briefly discussed some of the major current trends in hardware development, and below we will consider the effects of this development on software design. Moreover, we will touch upon how the evolution of methods and algorithms in itself affects the parallelization of applications. The combined effect of the advances in hardware and software is a rapidly evolving computational environment that poses a serious challenge for the program developer wishing to design long-lasting parallel software that will continue to take advantage of hardware performance gains; we will conclude this section with a discussion of new programming models that are designed to address this challenge.

#### 1.3.1 Responding to Changes in Hardware

In the past, efficient utilization of large-scale parallel computers has required adaptation of applications to accommodate a number of processors that doubled every three years. If the current trends continue to hold, however, the number of processors on parallel computers is expected to grow even faster, doubling every year. Thus, writing scalable applications, namely, parallel programs that can take advantage of a very large number of processors, becomes increasingly important. For example, this may entail putting more emphasis on reducing the communication overhead when designing parallel applications; using a significant amount of collective communication in a parallel application usually precludes scalability, and, moreover, the slower improvements in network performance than in instruction rates make it increasingly difficult to hide the communication overhead.

Although the rapidly increasing number of processors on the largest supercomputers emphasizes the need for efficient massively parallel applications, the increasing availability of small-scale parallel computers makes small-scale parallelism important as well. Small-scale parallelism is usually considerably easier to incorporate into a scientific application; achieving high parallel efficiency on a small number, perhaps a few tens, of processors may require relatively modest modifications to existing scalar code, whereas high parallel efficiency on thousands of processors requires a very carefully designed parallel application.

# 1.3.2 New Algorithms and Methods

Considering quantum chemistry in particular, hardware improvements have made it possible to tackle different classes of problems, posing a new set of challenges for parallel program developers. For instance, parallelization of Introduction 11

conventional quantum chemistry methods, whose computational cost scales as a high-degree polynomial in the molecular size, is rather forgiving in terms of what steps are parallelized. Consider, for example, conventional MP2 theory, whose computational cost is dominated by  $O(N^5)$  and  $O(N^4)$  steps for large N, where N is the size of the molecule. If the  $O(N^5)$  steps can be perfectly parallelized without communication overhead and the  $O(N^4)$  steps are run sequentially, then the time to solution, as a function of N and the number of processors, p, can be expressed as

$$t_{\text{MP2}}(N, p) \approx A \frac{N^5}{p} + B N^4$$

(1.1)

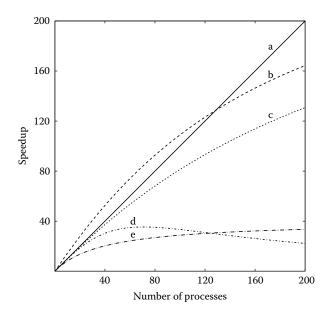

where A and B are constants and one process is run per processor. The fraction of time spent in serial code when running with a single process is  $f_{\text{MP2}} \approx B/(AN+B)$ , and from Amdahl's law (discussed in section 5.2.1) it then follows that the maximum attainable speedup is

$$S_{\text{max,MP2}} = \frac{1}{f_{\text{MP2}}} \approx \frac{AN + B}{B}.$$

(1.2)

The parallel efficiency (also defined in section 5.2.1), which measures how well the computer is utilized, is then given as

$$E_{\text{MP2}}(N, p) = \frac{t_{\text{MP2}}(N, 1)}{pt_{\text{MP2}}(N, p)} \approx \frac{1}{1 + \frac{(p-1)}{AN/B + 1}}$$

(1.3)

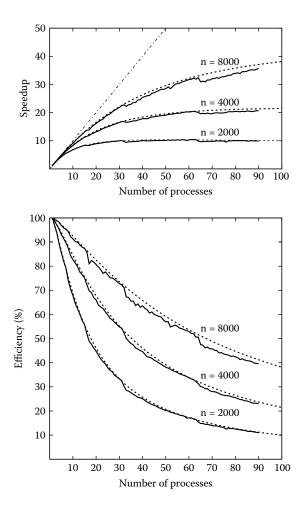

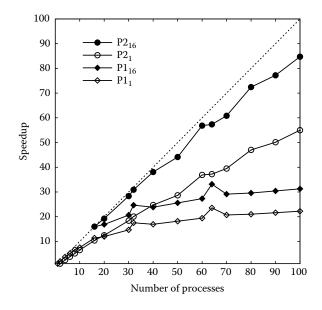

and a perfect parallelization corresponds to  $E_{\mathrm{MP2}}(N,p)=1$ . From Eq. 1.2 it follows that the maximum attainable speedup increases with the problem size. Also, we see from Eq. 1.3 that the efficiency decreases with the number of processors, but if the problem size increases at the same rate as the number of processors, the efficiency remains nearly constant. Thus, we can utilize a large number of processors with reasonably high efficiency provided that we have a large enough problem to solve. However, for a linear-scaling method, such as LMP2, we do not have such a luxury. Assuming that we have a linear-scaling algorithm with two linear-scaling terms, only one of which is parallelized, the time to solution is

$$t_{\rm LMP2}(N, p) \approx C \frac{N}{p} + DN \tag{1.4}$$

where C and D are constants. This yields the following maximum speedup and efficiency:

$$S_{\text{max,LMP2}} \approx \frac{C+D}{D} \tag{1.5}$$

$$E_{\text{LMP2}}(N, p) \approx \frac{1}{1 + \frac{(p-1)}{C/D+1}}.$$

(1.6)

In this case, there is a fixed upper limit to the achievable speedup, and the efficiency decreases as the number of processors increases, regardless of the problem size. Thus, much work must be invested to achieve efficient parallelization of linear-scaling methods; these methods involve a large number of steps that scale linearly in N, and each step must be parallelized to achieve high efficiency when running on large numbers of processors.

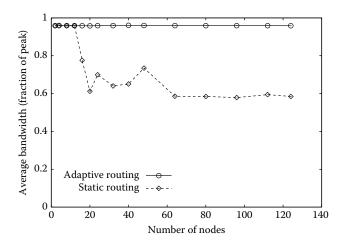

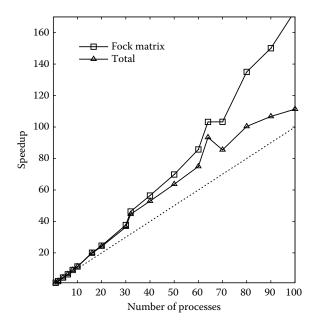

# 1.3.3 New Programming Models